ISSN: 2617-6548

URL: www.ijirss.com

# Design and manufacturing of digital integrated circuits tester at gate/flip flop level using Arduino mega platform

<sup>1</sup>Department of Electrical Engineering and Computer Science, College of Engineering, A Sharqiyah University, Ibra, Oman. <sup>2</sup>Department of Computer Engineering, Faculty of Engineering, Tishk International University, Erbil, Iraq.

Corresponding author: Yasir Hashim Naif (Email: yasir.hashim@ieee.org)

#### Abstract

This study paper aims to deliver a low-cost, computer-independent, and user-friendly 74, 54, and 4000-series logic Integrated Circuits (ICs) tester. Depending on the truth table of gates and the IC configuration, the logic IC tester will be able to test the function of those ICs' 74, 54, and 4000 series logic gates (NOR, OR, AND, NAND, XOR) and Flip-Flops (JK, D, T). The logic IC functional tester can be reprogrammed and updated depending on the flexibility provided by this design and using personal computer. The result of the testing of any 74-series IC will be displayed on liquid crystal display at unit level (gate or flip-flop). De-pending on the test results, the logic IC functional tester was successfully built and is fully operational.

Keywords: Arduino Mega, Digital IC, Logic gate, Testing IC.

DOI: 10.53894/ijirss.v8i7.10531

Funding: This study received no specific financial support.

**History: Received:** 12 August 2025 / **Revised:** 15 September 2025 / **Accepted:** 17 September 2025 / **Published:** 6 October 2025 **Copyright:** © 2025 by the authors. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

**Competing Interests:** The authors declare that they have no competing interests.

**Authors' Contributions:** All authors contributed equally to the conception and design of the study. All authors have read and agreed to the published version of the manuscript.

**Transparency:** The authors confirm that the manuscript is an honest, accurate, and transparent account of the study; that no vital features of the study have been omitted; and that any discrepancies from the study as planned have been explained. This study followed all ethical practices during writing.

Acknowledgment: The Authors are grateful to A'Sharqiyah university in Oman and Tishk International University (TIU) in Iraq for their valuable support.

**Publisher:** Innovative Research Publishing

## 1. Introduction

Development of intelligent systems around the world. Automatic systems have been widely used worldwide to improve and streamline thousands of people's daily lives [1-5]. The system for testing logic integrated circuits (ICs) capable of conducting gate- or unit-level tests will be made available by this study.

The International Technology Roadmap for Semi-conductors (ITRS) [6-9] states that manufacturing and design technologies are far ahead of testing. Tester technology will not improve if it stays at the same level [10]. The testing capacity of the tester is not keeping up with the rapid advancement of manufacturing technologies. Digital Integrated

Circuits (ICs) must undergo thorough testing in the electronic industry prior to being applied. When testing a digital integrated circuit (IC) that solely consists of a combinational logic gate or gates, the IC inputs are subjected to a few logic states, and the IC output is then assessed using the IC truth table.

Constructing an inexpensive, basic tool to evaluate logic integrated circuit functionality for manufacture, laboratory, or maintenance applications with the capacity to update the database is the main objective of the research on logic Integrated Circuits (IC) function-al testers [11, 12]. People without programming skills may write tests and use the system quickly and efficiently thanks to its user-friendly communication interface [13].

In addition, the system can function independently of a computer interface. To enable customers to access the results for later updates, the technology will also offer data storage. The tester system can be utilized with typical transistor-transistor logic (TTL) basic gates and flip-flop integrated circuits (ICs) [14]. To facilitate and enhance the power of IC testing, re-searchers have created programmable IC testers. If the microcontroller has been configured with a firmware that has the proper testing procedure, this task can be completed quickly using a programmable chip such as microcontroller.

The IC testers on the market right now cannot be easily reprogrammed to meet the needs of different users. Thus, the goal of this research is to create an inexpensive, user-friendly IC tester. The intention is to offer an IC tester at a reasonable cost for testing TTL logic ICs in the 74-series at the gate level. The test protocol will be grounded in the gates or flip -flops truth table in the ICs, facilitating the detection of mal-functioning gates or units in integrated circuits. The IC tester must also be compact, lightweight, portable, easy to use, and power efficient. The development of a simple and conveniently portable IC tester is the study's second goal. Furthermore, we want to provide an IC tester that makes results accessible to consumers.

Nowadays, nearly every laptop and desktop PC sold on the market has a Universal Serial Bus (USB) port. The purpose of this is to enable an IC tester to be programmed via the USB interface communication connector. A unified, user-friendly method of connecting to a computer is offered by the USB [15, 16].

Only a few preset levels or states are used by digital integrated circuits (ICs) for operation, as opposed to a continuous range of signal amplitudes. Modems, frequency counters, computers, and computer networks all use these parts [17, 18]. Logic gates are fundamental components of digital integrated circuits (ICs). They function on binary data, which is signals that have just two unique states: low (logic 0) and high (logic 1) [19-23].

During testing, the microcontroller assesses the IC output after sending certain logic states to the IC inputs. The microcontroller notifies the IC that everything is OK if the output matches the value recorded by the IC truth table. The microcontroller indicates that it's not good if not. An algorithm for this task has been proposed to researchers, who have subsequently implemented it for IC testers as a function for each type of digital IC. While in this paper, testing algorithms are implemented all types of combinational and sequential logic ICs.

#### 2. Methods

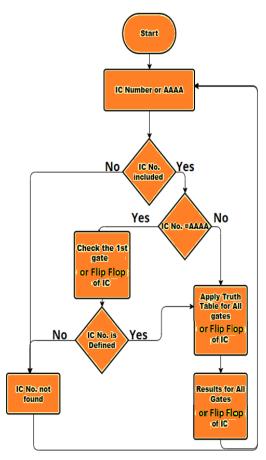

The flowchart of the system, shown in Fig. 1, basically provides a detailed explanation of how the system functions. This testing procedure flowchart served as the basis for the development of the algorithm and software. This flow chart indicates that entering IC No., or AAA for unidentified ICs, is the initial step. The following stage for the system is to test the IC using its truth table of gates after determining whether this IC No. is already in its database. As an alternative, if the user enters (AAAA) for unidentified ICs, the system will count the number of ICs and use the truth table to test each IC's gate after checking the initial gate for all ICs in line with the truth table.

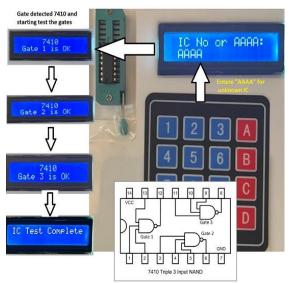

The flowchart indicates that if a user inputs an incorrect IC number, the message "IC not Found or IC not Work" will appear on the LCD. As shown in Fig. 2, if the user enters (AAAA) for undefined ICs, the IC number will be sought for by the system using the first gate's truth table exclusively for All ICs in the database, after locating the IC No., which is 7410, the system will test all the parts of the concerned IC using the No. that it has found. The system will first determine the IC number and start inspecting each gate separately if the user enters in (AAAA). In this example, the IC number was 7410 (a triple 3-input NAND gate).

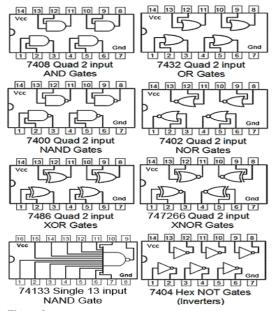

The pin configurations of the ICs 7400, 7408, 7486, and 7432 are identical, as seen in Fig. 3, each gate having two inputs and one output. In contrast, the pin design of the IC 7404 is entirely different, each gate having a single input and output. The adaptability of the system requires that each pin be reprogrammed as either an output or an input pin depending on the pin arrangement of the integrated circuit (IC) under test.

The Algorithm of the system will be as follows:

STEP1: START

STEP2: Enter the No. of 74-serios logic IC, or AAAA for unknown IC

STEP3: If the IC No. is known (74----), Then STEP7

STEP4: Arduino will test first gate (or unit) only by applying all truth tables to find the No. of IC

STEP5: If all truth tables fail with first gate, print ("IC No. NOT FOUND or IC NOT WORK"), Then STEP10

STEP6: If any of truth tables applied with the first gate, Then print (IC No.)

STEP7: Arduino will define the input and output pins depending on the pin configuration of IC

STEP8: Arduino check the truth table for each gate (or unit) inside IC

STEP9: Print the result for each gate (or unit) ("OK" or NOT OK") one by one

STEP10: Print ("THE TEST IS COMPLETE)

STEP11: END

The algorithm begins with the initial step where the user is prompted to start the testing process of a 74-series logic integrated circuit (IC). The first task is for the user to enter the specific number of the logic IC they wish to test. If the user encounters an unfamiliar IC, they are instructed to enter "AAAA" to signify that the IC number is unknown.

Next, the algorithm checks if the entered IC number follows the familiar 74-series format. If the number is recognized, the process moves to a testing phase. The Arduino system is programmed to focus on the first gate or unit of the IC, applying the relevant truth tables to identify the specific characteristics of the IC. This test involves systematically evaluating the logical operations that the gate should perform under various input conditions.

If all the truth table evaluations fail for the first gate, the system provides feedback by displaying a message that indicates the IC number cannot be found, or that the IC is not operational. Following this, the algorithm proceeds to the completion stage, where the testing process is summarized.

Conversely, if any of the truth table evaluations are successful, the algorithm acknowledges this by printing the identified IC number. The successful identification leads to defining the input and output pins of the IC based on its specific pin configuration. This is crucial because it allows the Arduino to interact correctly with the IC under test for subsequent evaluations.

Subsequently, the Arduino undertakes a thorough examination of the truth tables for each gate within the IC. This means that every individual gate or logical unit of the IC is subjected to input stimuli as specified by its truth table, enabling an evaluation of whether the outputs correspond to what is expected for the given inputs.

After processing each gate, the results are printed for the user to see. For every gate tested, the output will indicate "OK" if the gate is functioning correctly, or "NOT OK" if it does not meet the expected performance criteria. This step-by-step verification not only establishes the operational status of each gate within the IC but also contributes to an overall assessment of the IC's functionality.

Finally, after testing all the gates and printing the results, the algorithm concludes by displaying a message stating that "THE TEST IS COMPLETE." This serves as a final notification that the entire testing process has been conducted, and the results have been recorded.

The algorithm is an effective systematic approach for testing 74-series logic ICs, utilizing an Arduino's capabilities as both a signal generator and logic analyzer. This setup allows for hands-on experimentation with the ICs in a low-cost, efficient manner, making it an accessible option for students or individuals interested in learning about logic design and integrated circuits. Each step is designed to ensure clarity in identifying the operational status of the different gates within the IC, promoting a deeper understanding of digital logic design principles.

Ultimately, this algorithm illustrates a straightforward methodology for evaluating integrated circuits while empowering users to engage actively in the testing, ensuring a broad application in educational environments and DIY electronics projects. The combination of user interaction and systematic logic verification underscores the importance of practical experience in mastering electronic circuitry and design.

The flowchart (Figure 1) represents the systematic methodology employed for testing 74-series digital integrated circuits (ICs), which are widely used in logic design and digital system applications. The testing process begins with the input of an IC number or a generic identifier (AAAA). This step allows the system to differentiate between a specific IC from the 74xx family or a general case requiring broader truth table validation.

**Figure 1.** Flowchart of system.

The first decision block verifies whether the given IC number is included in the system's testing database. If the IC number is not recognized, the procedure terminates with an "IC No. not found" message, ensuring that only valid and supported ICs proceed further. When a valid IC number is included, the flowchart follows two distinct paths depending on the nature of the identifier.

If the input corresponds to a specific IC, the methodology proceeds by checking the first gate or flip-flop within the IC package. This step allows validation of basic functionality before extending the process to the remaining gates. The system then determines whether the IC is defined in the internal truth table library. If the IC is undefined, the process terminates, thereby avoiding unnecessary computation. If the IC is defined, the truth table corresponding to that IC is applied, and the system generates output results for all the gates or flip-flops contained in the device.

Alternatively, if the identifier is the placeholder AAAA, representing a generic testing case, the system bypasses the preliminary gate-level validation. Instead, it directly applies the stored truth table for all possible gate or flip-flop configurations within the 74-series library. This approach ensures flexibility in handling both device-specific and generic test scenarios.

From a research perspective, this methodology demonstrates a structured and automated approach to functional verification of 74-series digital ICs. The hierarchical decision-making process enhances efficiency by filtering out undefined devices early in the workflow. At the same time, the incorporation of both specific and generic test pathways ensures broad applicability. Such a testing framework can be integrated into laboratory educational tools, automated IC testing equipment, and digital system validation platforms, thereby reducing manual verification time and minimizing human error.

**Figure 2.**User enters AAAA for the unknown IC test.

Figure 3. 74-series logic ICs configuration used in this research (Examples).

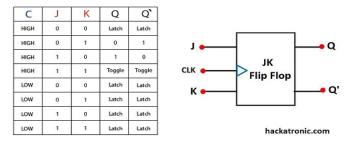

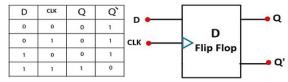

As a result, following entry of the IC number by the user, the microcontroller pins will be reprogrammed by the system as in or out pins to match the IC configuration depending on IC number. The truth table for each gate will then be applied by the system to ascertain whether or not it functions under the required conditions. Examples of the truth tables that the system uses for each gate and Flip- Flop are shown in Figures 4 and 5.

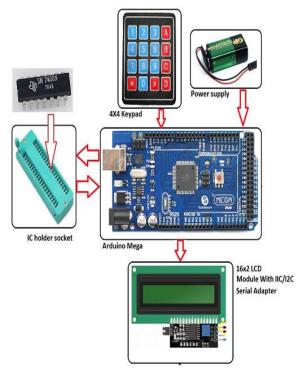

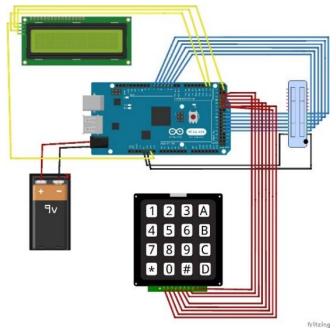

Figure 6 displays the system block diagram. There are four components that comprise the system. The first and main component is the Arduino Mega platform module [24], The Arduino Mega serves as the system's main microcontroller. The Arduino Mega includes 54 programmable logic inputs and outputs, numbered from 0 to 53. As a result, a variety of logic integrated circuits (ICs) with larger pin sizes can be tested using it.

Truth tables for logic gates (Examples).

### Truth Table of JK Flip Flop

## Truth Table of DFlip Flop

**Figure 5**. Truth tables for JK and D Flip-Flops (Examples).

Figure 7 displays the IC testing system's circuit schematic. It is comprised of an Arduino Mega board, which acts as a microcontroller and connects to an IC holder with 40 pins, a four-by-four keypad [25] to input the intended IC number for testing, an LCD module (16 by 2) [26, 27] that displays each IC gate's test results, the IC holder, and a 9-volt battery that powers everything.

Figure 6.

The system is depicted as a block diagram

**Figure 7.** Circuit diagram of the system

## 3. Result and Discussion

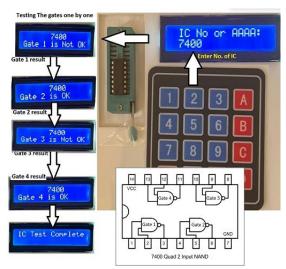

The system has been tested for wide range of logic ICs and the test results show the great precision for gate-level testing of these integrated circuits. The results of testing were as follows: Testing of the 7400 logic IC (quad 2-input NAND gate IC) with malfunctioning first and third gates and functional second and fourth gates is shown in Figure 8.

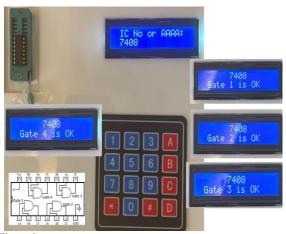

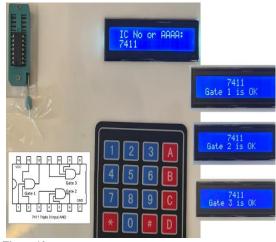

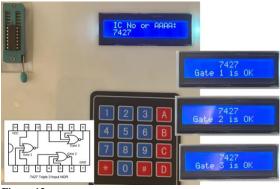

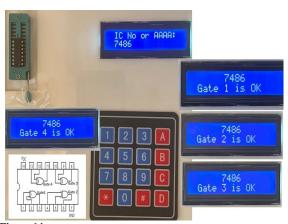

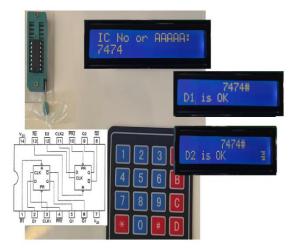

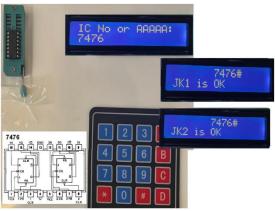

Figure 9, 10, 11, 12, 13 and 14, shows the test of 7408 (2 inputs quad AND gates IC), 7411 (3-input triple AND gates IC), 7420 (4 inputs dual NAND gates IC), 7421 (4 input dual AND gates IC), 7427 (3 input triple NOR gates IC), 7486 (2 inputs quad XOR gates IC), all these ICs with no faults conditions for all gates. Figures 15,16 show the results of tests of D and JK flip-flops with no fault conditions for all flip-flops for both ICs. Table 1 lists every logic 74-series integrated circuit that the system has tested and found to be outstanding.

**Figure 8.** First and third gates in the 7400 IC test are not functioning properly.

**Figure 9.** All four AND gates in the 7408 IC test function normally

Figure 10. All three (AND) gates in the 7411 IC test function normally

Figure 11.

All three AND gates in the 7411 IC test work normally.

Figure 12.

Two AND gates in the 7421 IC test operate normally.

Figure 13.

In the 7427 IC test, each of the three NOR gates operate as intended

Figure 14.

In the 7486 IC test, each of the four XOR gates operate as intended.

**Figure 15.** The 7476 IC test, each of the dual D flip-flops operates as intended

**Figure 16**. The 7474 IC test, each of the dual JK flip-flops operate as intended.

Table 1.

Tested ICs

| Description               | Company code |

|---------------------------|--------------|

| 2 inputs quad NAND gates  | SN74LS00     |

| 2 inputs quad NOR gates   | SN74LS02     |

| six inverter gates        | SN74LS04     |

| 2 inputs quad AND gates   | SN74LS08     |

| 3 input triple NAND gates | SN74LS10     |

| 3-input triple AND gates  | SN74LS11     |

| 4 inputs dual NAND gates  | SN74LS20     |

| 4 input dual AND gates    | SN74LS21     |

| 3 input triple NOR gates  | SN74LS27     |

| 2 inputs quad XOR gates   | SN74LS86A    |

| Dual JK negative edge FF  | SN74S122N    |

| Dual JK Flip Flos         | NTE74LS76A   |

| Dual D positive edge FF   | SN74LS74N    |

| Dual JK negative edge FF  | SN74S73AN    |

## 4. Result and Discussion

The goal of this research is to design and develop 74-series logic integrated circuits at unit level (gate or flip-flop). The Arduino Mega platform was used to develop this system as microcontroller. The Arduino Mega platform features 54 pins that can be configured as in or out pins to handle ICs with sizes ranging from 4 to 40 pins. It has been used to test many logic ICs, and the results indicate that the conditions of the ICs are well matched.

# References

[1] Y. Hashim, "Automatic control system of highway lights," *TELKOMNIKA Telecommunication, Computing, Electronics and Control*, vol. 18, no. 6, pp. 3123-3129, 2020. https://doi.org/10.12928/telkomnika.v18i6.16497

- [2] S. P. Lau, G. V. Merrett, A. S. Weddell, and N. M. White, "A traffic-aware street lighting scheme for Smart Cities using autonomous networked sensors," *Computers & Electrical Engineering*, vol. 45, pp. 192-207, 2015. https://doi.org/10.1016/j.compeleceng.2015.06.011

- [3] C. P. Janssen, S. F. Donker, D. P. Brumby, and A. L. Kun, "History and future of human-automation interaction," *International Journal of Human-Computer Studies*, vol. 131, pp. 99-107, 2019. https://doi.org/10.1016/j.ijhcs.2019.05.006

- [4] B. Berberian, J.-C. Sarrazin, P. Le Blaye, and P. Haggard, "Automation technology and sense of control: A window on human agency," *PLOS ONE*, vol. 7, no. 3, p. e34075, 2012. https://doi.org/10.1371/journal.pone.0034075

- [5] S. Madakam, R. M. Holmukhe, and D. K. Jaiswal, "The future digital work force: Robotic process automation (RPA)," JISTEM-Journal of Information Systems and Technology Management, vol. 16, p. e201916001, 2019. https://doi.org/10.4301/S1807-1775201916001

- [6] Y. Hashim and S. Mawlood, "Si-and Ge-FinFET inverter circuits optimization based on driver to load transistor fin ratio," *Journal of Nano-and Electronic Physics*, vol. 13, no. 6, 06011, 2021. https://doi.org/10.21272/jnep.13(6).06011

- [7] P. D. Fisher and R. Nesbitt, "The test of time. Clock-cycle estimation and test challenges for future microprocessors," *IEEE Circuits and Devices Magazine*, vol. 14, no. 2, pp. 37-44, 1998. https://doi.org/10.1109/101.666590

- [8] K. N. Devika and R. Bhakthavatchalu, "Design of efficient programmable test-per-scan logic BIST modules," in 2017 International conference on Microelectronic Devices, Circuits and Systems 2017. https://doi.org/10.1109/ICMDCS.2017.8211609.

- [9] B. Pradarelli, L. Latorre, M. L. Flottes, Y. Bertrand, and P. Nouet, "Remote labs for industrial IC testing," *IEEE Transactions on Learning Technologies*, vol. 2, no. 4, pp. 304-311, 2009. https://doi.org/10.1109/TLT.2009.46

- [10] C.-H. Yeh, J.-E. Chen, C.-J. Chang, and T.-C. Huang, "Using enhanced test systems based on digital IC test model for the improvement of test yield," *Electronics*, vol. 11, no. 7, p. 1115, 2022. https://doi.org/10.3390/electronics11071115

- [11] Y. Atalla, Y. Hashim, and A. N. A. Ghafar, "The impact of channel fin width on electrical characteristics of Si-FinFET," *International Journal of Electrical and Computer Engineering*, vol. 12, no. 1, pp. 201–207, 2022.

- [12] Y. Hashim, "Temperature effect on ON/OFF current ratio of FinFET transistor," in 2017 IEEE Regional Symposium on Micro and Nanoelectronics (RSM), 2017, https://doi.org/10.1109/RSM.2017.8069160.

- [13] Y. H. Chen, C. M. Hsu, and K. J. Lee, "Testchips with scan-based logic arrays," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 40, no. 4, pp. 790-802, 2021. https://doi.org/10.1109/TCAD.2020.3010478

- [14] M. S. Ahmed, I. M. Umair, and K. Mehboob, "Microcontroller Based IC Tester," in 2005 Student Conference on Engineering Sciences and Technology, 2005. https://doi.org/10.1109/SCONEST.2005.4382884.

- [15] L. Ali, R. Sidek, I. Aris, M. A. M. Ali, and B. S. Suparjo, "Design of a low cost IC tester," *American Journal of Applied Sciences*, vol. 2, no. 4, pp. 824-827, 2005.

- [16] L. Ali, R. Sidek, I. Aris, B. Sunaryo Suparjo, and M. Alauddin Mohd. Ali, "Challenges and directions for testing IC," *Integration*, vol. 37, no. 1, pp. 17-28, 2004. https://doi.org/10.1016/j.vlsi.2003.09.006

- [17] K. Vanitha and C. A. Sathiya Moorthy, "Implementation of an integrated FPGA based automatic test equipment and test generation for digital circuits," in 2013 International Conference on Information Communication and Embedded Systems (ICICES), 2013. https://doi.org/10.1109/ICICES.2013.6508284.

- [18] D. R. Krishna, L. R. Krishna, D. S. Kumar, and P. S. Sunil, "Microprocessor based digital IC tester," *IETE Journal of Education*, vol. 26, no. 3, pp. 105-110, 1985. https://doi.org/10.1080/09747338.1985.11436066

- [19] F. Van Veen, "An introduction to IC testing," *IEEE Spectrum*, vol. 8, no. 12, pp. 28-37, 1971. https://doi.org/10.1109/MSPEC.1971.5217887

- [20] B. Xiao, X. Li, Y. Lin, and Y. Zhang, "Design and application of an IC chip test instrument based on HT46RU24," in 2021 International Symposium on Computer Technology and Information Science (ISCTIS), 2021. https://doi.org/10.1109/ISCTIS51085.2021.00056.

- [21] B. Rabakavi and S. Siddamal, "Design of high speed, reconfigurable multiple ICs tester using FPGA platform," in 2018 International Conference on Electrical, Electronics, Communication, Computer, and Optimization Techniques, 2018. https://doi.org/10.1109/ICEECCOT43722.2018.9001588.

- [22] Y. C. Chang *et al.*, "Design of the multifunction IC-EMC test board with off-board probes for evaluating a microcontroller," in 2015 Asia-Pacific Symposium on Electromagnetic Compatibility, 2015. https://doi.org/10.1109/APEMC.2015.7175301.

- [23] H. M. Ali, Y. Hashim, and G. A. Al-Sakkal, "Design and implementation of Arduino based robotic arm," *International Journal of Electrical and Computer Engineering*, vol. 12, no. 2, p. 1411, 2022. http://doi.org/10.11591/ijece.v12i2.pp1411-1418

- [24] Z. M. Livinsa, G. M. Valantina, M. G. Premi, and G. M. Sheeba, "A modern automatic cooking machine using arduino mega and IOT," in *Journal of Physics: Conference Series*, 2021.

- [25] A. Z. Jidin, N. M. Yusof, and T. Sutikno, "Arduino based paperless queue management system," *Telecommunication Computing Electronics and Control*, vol. 14, no. 3, pp. 839-845, 2016. http://doi.org/10.12928/telkomnika.v14i3.3114

- [26] I. J. Hasan, B. M. Waheib, N. A. J. Salih, and N. I. Abdulkhaleq, "A global system for mobile communications-based electrical power consumption for a non-contact smart billing system," *International Journal of Electrical and Computer Engineering*, vol. 11, no. 6, p. 4659, 2021.

- [27] A. L. Dewi, J. E. Suseno, and Q. M. B. Soesanto, "Measurement device of nondestructive testing (NDT) of metanil yellow dye waste concentration using artificial neural network based on microcontroller," *IEEE Sensors Letters*, vol. 6, no. 8, pp. 1-4, 2022. https://doi.org/10.1109/LSENS.2022.3192865